2030年芯片晶体管达万亿规模!TSMC制程与封装技术双向推进

在最近的IEDM会议上,台积电TSMC展示了一个包含一万亿个晶体管的发展路线图,这一计划与去年英特尔透露的计划相似。这些超大规模的芯片将利用先进的封装技术,将多个单颗芯片集成在一起。

2030年芯片晶体管达万亿规模

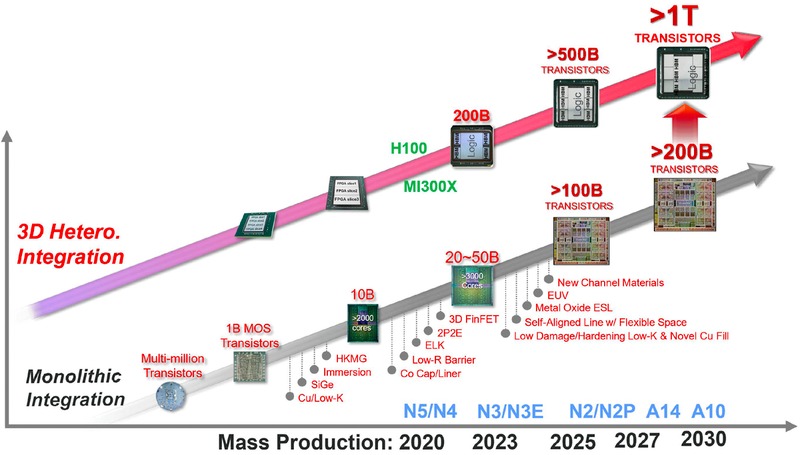

在最近的IEDM会议上,台积电TSMC展示了一个包含一万亿个晶体管的发展路线图,这一计划与去年英特尔透露的计划相似。这些超大规模的芯片将利用先进的封装技术,将多个单颗芯片集成在一起。同时,台积电还正在努力开发具有2000亿个晶体管的单个芯片。为了实现这一目标,该公司确认正在研发2纳米级的N2和N2P生产节点,并计划在2030年推出1.4纳米级的A14和1纳米级的A10制造工艺。

台积电的发展路线图在IEDM会议上展示了对封装技术的前景预测。近年来,随着芯片制造商面临技术和财务挑战,领先工艺技术的研发速度有所放缓。台积电面临与其他公司相同的挑战,然而作为全球最大的晶圆代工厂商,台积电有信心在未来五到六年内提升其生产节点的性能、功耗和晶体管密度,并推出2纳米、1.4纳米和1纳米的节点。

根据台积电的说法,英伟达的拥有800亿个晶体管的GH100是市场上最复杂的单芯片处理器之一,而且预计会很快出现更多拥有超过1000亿个晶体管的复杂单芯片。然而,制造如此庞大的处理器变得越来越复杂和昂贵,因此许多公司选择采用多芯片设计。例如,AMD的Instinct MI300X和英特尔的Ponte Vecchio都由数十个芯片组成。

在芯片设计越来越复杂、集成度越来越高的趋势下,台积电需要与其代工客户的需求保持同步。因此,台积电将在工艺制程和封装技术两个方面继续进行创新。更先进的工艺可以带来更高的晶体管密度,而更先进的封装技术则可以加快芯片规模的扩大。数年后,我们将会看到由超过一万亿个晶体管组成的多芯片解决方案,并且会看到具备高达2000亿个晶体管的单芯片处理器的出现。

-

2

狗生模拟器破解版内置修改器v1.0.12

休闲益智

查看